## An Efficient Architecture for Closed–Loop Power–Control Access

by

Brandon C. Brown

### Bachelor of Applied Science, Queen's University, 2006

### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### Master's of Electrical Engineering

In the Graduate Academic Unit of Electrical and Computer Engineering

| Supervisors:     | Mary E. Kaye, M.Eng., Electrical and Computer Engineering     |

|------------------|---------------------------------------------------------------|

|                  | Brent R. Petersen, Ph.D., Electrical and Computer Engineering |

| Examining Board: | Christopher P. Diduch, Ph.D.,                                 |

|                  | Electrical and Computer Engineering, Chair                    |

|                  | Howard Li, Ph.D., Electrical and Computer Engineering         |

|                  | Kenneth B. Kent, Ph.D., Faculty of Computer Science           |

This thesis is accepted

Dean of Graduate Studies

### THE UNIVERSITY OF NEW BRUNSWICK

#### September, 2009

© Brandon C. Brown, 2009

To Mom and Dad

# Abstract

In this thesis a cost-effective means to gain access to wireless communication channels is proposed and implemented. A testbed is created using mostly commercial off-the-shelf components, and the signal processing is implemented in an Altera® DE– 3 development board, which includes Altera®'s Stratix III® field programmable gate array, as well as two Terasic® ADA boards which provide analog-to-digital and digital-to-analog conversions. Modulation and demodulation was performed on both the forward and reverse channels to bring the signals to an intermediate frequency such that no low pass filter was needed before the signal was acquired by the development board. Testing showed that the CDMA power-control algorithm was able to perform within acceptable limits, and that the implemented system was nearly transparent to both the mobile and the base station. To demonstrate how the system could be used, non-uniform sampling was also implemented in a variety of ways, which included a simple method of incrementally introducing noise.

# Acknowledgements

First and foremost, I would like to extend my thanks and gratitude to my supervisors Brent R. Petersen and Mary E. Kaye for all the guidance and assistance they afforded me throughout my research.

I would also like to thank all of the Electrical and Computer Engineering technical staff for their help with the circuit board fabrication, mounting the final project, and the many other various technical aspects of project implementation that they assisted with.

This research was supported by the Atlantic Innovation Fund from the Atlantic Canada Opportunities Agency, and by Bell Aliant, our industrial partner.

# **Table of Contents**

| $\mathbf{A}$               | bstra  | ct                                | iii      |

|----------------------------|--------|-----------------------------------|----------|

| A                          | cknov  | wledgments                        | iv       |

| Τa                         | able o | of Contents                       | v        |

| $\mathbf{Li}$              | st of  | Figures                           | viii     |

| $\mathbf{Li}$              | st of  | Abbreviations                     | х        |

| 1                          | Intr   | oduction                          | 1        |

|                            | 1.1    | Background                        | 1        |

|                            | 1.2    | Problem                           | 2        |

|                            | 1.3    | Objective                         | 2        |

|                            | 1.4    | Contributions                     | 3        |

| 2 Overview of Architecture |        |                                   | <b>5</b> |

|                            | 2.1    | Description of System             | 5        |

|                            | 2.2    | Overall Requirements Analysis     | 6        |

|                            |        | 2.2.1 Baseband Data Transfer Rate | 6        |

|                            | 2.3    | Architecture Design Iterations    | 7        |

|                            |        | 2.3.1 Initial Designs             | 7        |

|                            |        | 2.3.2 Final Idea                  | 8        |

| 3                          | Har    | dware Selection                   | 10       |

|                            | 3.1    | Clock Sources                     | 10       |

|                            | 3.2    | Individual Part Requirements      | 11       |

|                            |        | 3.2.1 Modulators and Demodulators | 11       |

|                            |        | 3.2.2 FPGA and Daughter Cards     | 11       |

|                            | 3.3    | System Power Requirements         | 12       |

|                            | 3.4    | Amplifiers                        | 12       |

| 4                          | Imp    | lementation                       | 14       |

|                            | 4.1    | Selected Parts                    | 14       |

|                            |        | 4.1.1 FPGA Development Board      | 14       |

|                            |        | 4.1.2 Modulators and Demodulators | 14       |

|              | 4.2            | Bias Board                                                                                    | j |

|--------------|----------------|-----------------------------------------------------------------------------------------------|---|

|              | 4.3            | Frequency Selection                                                                           | 7 |

|              | 4.4            | Clock Synchronization                                                                         | 3 |

|              | 4.5            | RF Isolation                                                                                  | 3 |

|              |                |                                                                                               |   |

| <b>5</b>     | Tes            | ting 19                                                                                       |   |

|              | 5.1            | Bias Boards                                                                                   | ) |

|              | 5.2            | Modulator                                                                                     | ) |

|              | 5.3            | Demodulator                                                                                   | ) |

|              | 5.4            | FPGA 22                                                                                       | 2 |

|              | 5.5            | CDMA/EVDO Transparency 25                                                                     | ý |

| 0            | <b>N</b> T     |                                                                                               | - |

| 6            |                | n-Uniform Sampling 27                                                                         |   |

|              | 6.1            | Mathematical Model                                                                            |   |

|              | 6.2            | Implementation                                                                                |   |

|              | 6.3            | Known Signal Tests                                                                            |   |

|              |                | $6.3.1  \text{Test Results}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |   |

|              | 0.4            | 6.3.2 Discussion                                                                              |   |

|              | 6.4            | Application to Architecture                                                                   |   |

|              | 6.5            | Noise Parameter Discovery   41                                                                |   |

|              |                | 6.5.1 Modification to PN Generator                                                            |   |

|              |                | 6.5.2 Length of Shift Register                                                                |   |

|              |                | 6.5.3 Relation to Theoretical Results                                                         |   |

|              |                | 6.5.4 Effect on CDMA/EVDO Traffic                                                             | ) |

| 7            | Sur            | nmary and Future Work 51                                                                      |   |

| •            | 7.1            | Summary of Completed Work                                                                     |   |

|              | 7.2            | Future Work   52                                                                              |   |

|              | 1.2            |                                                                                               | 1 |

| $\mathbf{A}$ | ppen           | dices 56                                                                                      | ; |

|              |                |                                                                                               | _ |

| Α            | Bia            | s Board Schematic 56                                                                          | ) |

| В            | Dot            | ailed Wiring Diagram 57                                                                       | 7 |

| D            | Det            | and Wiring Diagram 57                                                                         |   |

| $\mathbf{C}$ | $\mathbf{Fin}$ | al Project Functional Design 59                                                               | ) |

| -            |                |                                                                                               | _ |

| D            |                | TLAB <sup>®</sup> Code Listing 60                                                             | - |

|              |                | spec1.m                                                                                       |   |

|              | D.2            | pb2.m                                                                                         |   |

|              | D.3            | pb1.m                                                                                         |   |

|              | D.4            | pulsef.m                                                                                      |   |

|              | D.5            | pulser.m                                                                                      |   |

|              | D.6            | rect.m                                                                                        |   |

|              | D.7            | zero.m                                                                                        |   |

|              | D.8            | one.m                                                                                         | 3 |

|              | D.9                            | $function\_feeder.m$         | 64  |

|--------------|--------------------------------|------------------------------|-----|

| $\mathbf{E}$ | Veri                           | ilog Code and Block Diagrams | 66  |

|              | E.1                            | Code Used in Section 6.3     | 66  |

|              |                                | E.1.1 jitter6BitBuff.v       | 66  |

|              |                                | E.1.2 jitter6BitBuffEven.v   | 68  |

|              |                                | E.1.3 jitter6BitBuffSingle.v | 70  |

|              |                                | E.1.4 jitter6BitBuffTight.v  | 72  |

|              | E.2                            | Code Used in Section 6.5.1   | 74  |

|              |                                | E.2.1 jitterMultiPN.v        | 74  |

|              |                                | E.2.2 pnGenerator3bit.v      | 75  |

|              |                                | E.2.3 pnGenerator4bit.v      | 76  |

|              |                                | E.2.4 pnGenerator5bit.v      | 77  |

|              |                                | E.2.5 pnGenerator6bit.v      | 79  |

|              |                                | E.2.6 pnGenerator7bit.v      | 80  |

|              |                                | E.2.7 pnGenerator8bit.v      | 81  |

|              |                                | E.2.8 pnGenerator9bit.v      | 82  |

|              |                                | E.2.9 pnGenerator10bit.v     | 84  |

|              |                                | E.2.10 DE3.v                 | 85  |

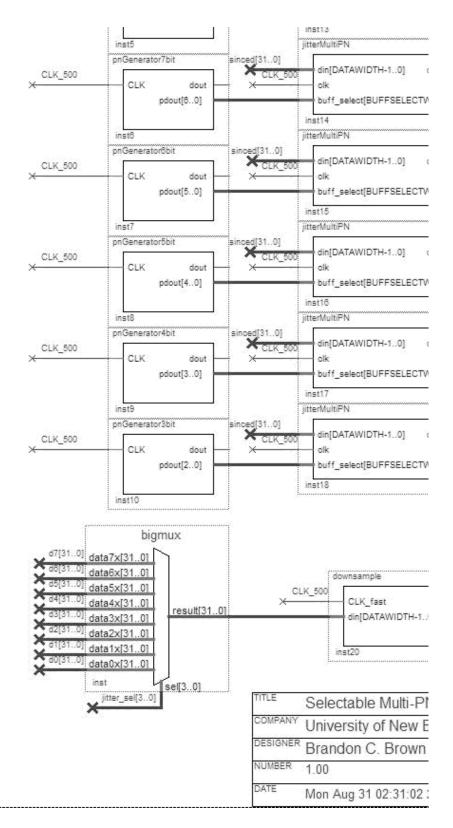

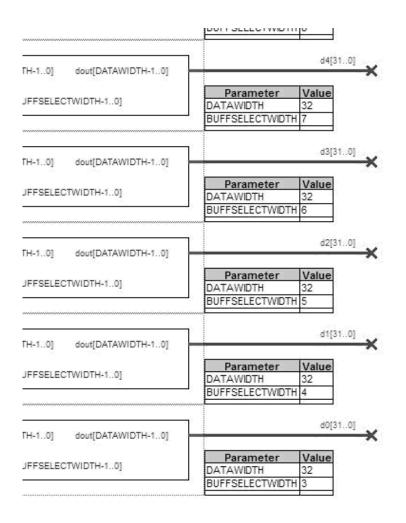

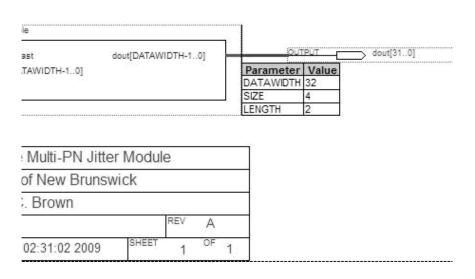

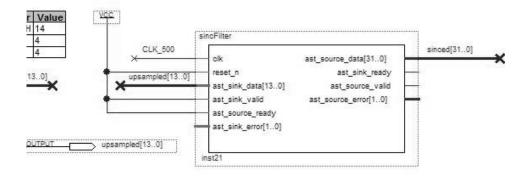

|              |                                | E.2.11 Block Diagram         | 92  |

|              | E.3 Code Used in Section 6.5.2 |                              |     |

|              |                                | E.3.1 DE3.v                  | 97  |

|              |                                | E.3.2 jitterUniform3Regs.v   | 103 |

|              |                                |                              | 104 |

|              |                                |                              | 105 |

|              |                                | E.3.5 jitterUniform25Regs.v  | 106 |

|              |                                |                              | 108 |

|              |                                |                              | 10  |

|              |                                |                              |     |

Vita

# List of Figures

| 2.1  | High-level proposal                                                                |

|------|------------------------------------------------------------------------------------|

| 2.2  | Initial design idea.                                                               |

| 2.3  | Functional diagram for the final design                                            |

| 4.1  | Signal biasing board                                                               |

| 5.1  | Test setup for testing the Inphase                                                 |

| 5.2  | Test setup for fully testing the modulator                                         |

| 5.3  | Spectral output from the modulator                                                 |

| 5.4  | FPGA test setup                                                                    |

| 5.5  | Resulting spectrum of a 10 MHz signal passing through the FPGA 23                  |

| 5.6  | A 10 MHz input signal directly from the clock source used without                  |

|      | passing through the architecture                                                   |

| 5.7  | Data being transmitted during an FTAP test through the system 25                   |

| 5.8  | A successful power-control test                                                    |

| 6.1  | Non-uniform sampling implementation                                                |

| 6.2  | Showing the maximum value (top line), an instantaneous reading (mid-               |

|      | dle line), and the minimum value (bottom line) of a 10 MHz signal                  |

| 69   | using uniform sampling                                                             |

| 6.3  | A normal distribution showing how many times each register is called<br>per period |

| 6.4  | Showing the maximum value (top line), an instantaneous reading (mid-               |

| 0.1  | dle line), and the minimum value (bottom line) of a 10 MHz signal                  |

|      | using non-uniform sampling                                                         |

| 6.5  | Modified distribution                                                              |

| 6.6  | The resulting maximum value (top line), an instantaneous reading                   |

|      | (middle line), and the minimum value (bottom line) of the spectrum                 |

|      | using the modified normal distribution                                             |

| 6.7  | The nearly even distribution used for register selection                           |

| 6.8  | The resulting maximum value (top line), an instantaneous reading                   |

|      | (middle line), and the minimum value (bottom line) of the spectrum                 |

|      | using the nearly even distribution                                                 |

| 6.9  | Noise dominating both forward and reverse channels                                 |

| 6.10 | An Implementation of non–uniform sampling                                          |

| 6.11 | Output when equation 6.33 was implemented                                          |

| 6.12 | Output when equation 6.26 was implemented                     | 45  |

|------|---------------------------------------------------------------|-----|

| 6.13 | Output for 3 registers.                                       | 46  |

| 6.14 | Output for 5 registers.                                       | 47  |

| 6.15 | Output for 25 registers                                       | 48  |

| 6.16 | Data transfer with non–uniform sampling noise added           | 50  |

| A.1  | Bias board schematic.                                         | 56  |

| B.1  | Wire connections                                              | 58  |

| C.1  | Functional design of the final project                        | 59  |

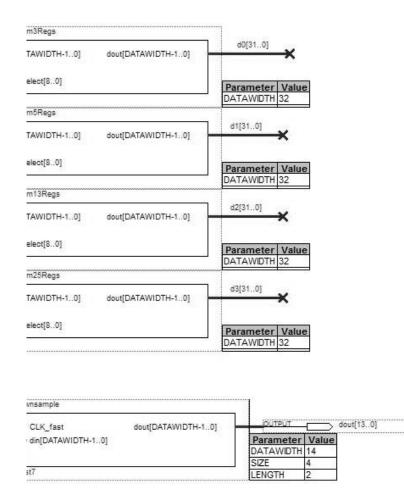

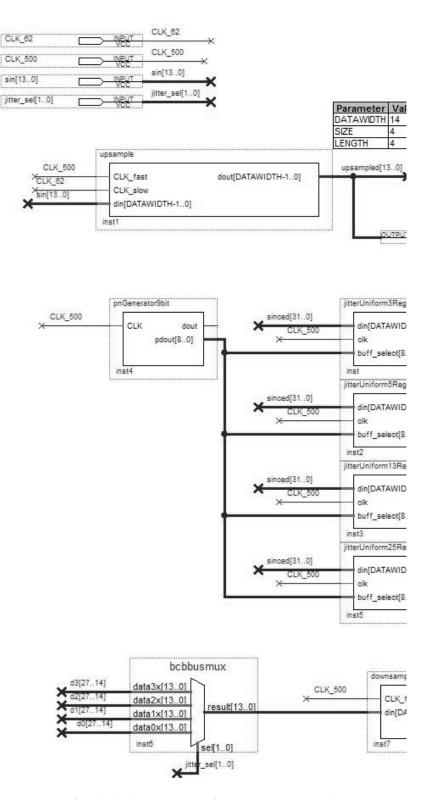

| E.1  | Part 1 of 4: block diagram of the Verilog implementation used | 93  |

| E.2  | Part 2 of 4: block diagram of the Verilog implementation used | 94  |

| E.3  | Part 3 of 4: block diagram of the Verilog implementation used | 95  |

| E.4  | Part 4 of 4: block diagram of the Verilog implementation used | 96  |

| E.5  | Part 1 of 2: block diagram of the Verilog implementation used | 111 |

| E.6  | Part 2 of 2: block diagram of the Verilog implementation used | 112 |

# List of Abbreviations

| AI | DC                   | Analog–to–Digital Converter        |

|----|----------------------|------------------------------------|

| CI | DMA                  | Code Division Multiple Access      |

| CO | OTS                  | Commercial off the Shelf           |

| DA | AC                   | Digital–to–Analog Converter        |

| dE | 3                    | DeciBels                           |

| dE | Bm                   | DeciBels relative to one milliwatt |

| E١ | VDO                  | Evolution-Data Optimized           |

| FF | PGA                  | Field Programmable Gate Array      |

| GI | PIO                  | General Purpose Input/Output       |

| Ι  |                      | Inphase                            |

| IF |                      | Intermediate Frequency             |

| kb | $\operatorname{ops}$ | Kilo-bits per second               |

| LF | PF                   | Low Pass Filter                    |

| M  | bps                  | Mega-bits per second               |

| Ms | $\operatorname{sps}$ | Mega-samples per second            |

| 00 | CXO                  | Oven Controlled Crystal Oscillator |

| PC | СВ                   | Printed Circuit Board              |

| PC | CS                   | Personal Communications Services   |

| PN | N                    | Psudorandom Number                 |

| PS | SU                   | Power Supply Unit                  |

|    |                      |                                    |

| Q                   | Quadrature                        |

|---------------------|-----------------------------------|

| RTAP                | Reverse Test Application Protocol |

| $\operatorname{RF}$ | Radio Frequency                   |

| $V_{\rm DC}$        | Voltage Direct Current            |

# Chapter 1

## Introduction

### 1.1 Background

In a CDMA system, all mobile stations must be received by the base station at the same power. If one mobile station were to be stationed next to the base station and transmitting at full power, the base station would not be able to detect the other mobiles which are further away. One of the most used solutions to mitigate this *near-far* problem is power control [1].

Several types of power control are available, such as the ones simulated by Chulajata and Kwon, who showed that by combining more than one power control algorithm it was possible to increase performance [2]. However, as is shown by Sim et al. it is possible to lower the bit error rate of a moving mobile station by simply updating the power control more frequently but at the cost of using increased resources [3].

CDMA is a spread spectrum technology that originally had its background in military applications providing secure communications [4]. The standard started as IS95, and has since evolved to its current form seen today: cdma2000. EVDO was integrated with cdma2000 to provide high rate data packet services without having to support old standards [5]. This project utilizes the CDMA/EVDO technology as a basis for communication between the mobile and the base station.

Time–varying channel conditions are also present in CDMA systems, which requires the power control algorithm to respond accordingly to ensure communication continues, as well as signal filters to remove possible multipath effects. Channel fading generally follows Rayleigh or Ricean fading distributions, and consists of flat fading or fading in the small scale [1].

### 1.2 Problem

The communication medium used by cellular CDMA systems for power control is a closed system; the relationship between the transmitter and receiver is such that it is not meant to have a third party join the communication or modify the channel. In order to gain access into the communication stream, a system must be set up in order to intercept the signal sent from a mobile station to the base station and vice versa. Once the signal is captured (and possibly modified), having it continue back through the original transmission medium will be required to make it appear to both devices as if the system is transparent.

### 1.3 Objective

The objective of the proposed research consists of designing and implementing a system in which it is possible to capture and retransmit the communication between a mobile station and a CDMA base station. The solution is implemented using as many COTS components as possible.

The motivation for developing this system is to analyze both the forward and reverse links simultaneously. Modern mobile phones are able to separate the forward and reverse links internally using customized proprietary hardware. Because of this it is impossible to gain access or control of the phone's hardware.

There are other systems which have been designed or implemented which perform similar functions to the system proposed in this thesis, each with their own benefits and drawbacks. Niida et al. had an entire cell phone network set up with multiple base transceiver stations and multiple mobile stations [6]. An ultra wideband transceiver prototyping test bed has also been built, but requires 8 high speed ADCs to capture signals using time samples, not frequency shifting, at sampling rates of up to 8 GHz [7]. Also, the emphasis in the research was on the demodulation only. Another design by Shono et al. has a transceiver architecture with a digital signal processor at its core, and was designed for the IEEE 802.11 standard, however it did not use an explicit modulator or demodulator [8].

In order to gain access to both the forward and reverse channels, the signal will have to be demodulated, passed through a device which is controllable such as an FPGA, and then modulated back up to RF. With this system it should be possible to monitor the transmission that is being sent by the base station to the mobile station and vice–versa. It could also allow researchers to modify the captured signal to determine if that signal can be controlled externally. Also, using this system it may be possible to model the channel and possibly evaluate current power-control algorithms and phone performance.

### **1.4** Contributions

The architecture put forth in this research will serve as a test bed for future research on mobile communications channels. Since the forward and reverse link channels are separated and handled individually within the FPGA it is possible to apply channel conditions to only one channel at a time. This gives the ability to clearly see how a test condition on one channel can potentially affect the other channel. The purpose of this system is to allow researchers to view the communications channel while in real world conditions and allow modifications to the channels. Using the system proposed it may also be possible to obtain data on the channel characteristics from these measurements.

After dominion over the power-control is established it would be possible to test alternative power-control algorithms in a real-world scenario and compare the results to well established algorithms. Also, because it would be possible to assert a channel model, the ability to test to see under what conditions current power-control algorithms fail becomes a possible use of this architecture.

To help save complexity and to help ensure that as little signal is lost as possible, the LPFs in the original design were removed. In order to do this the guarantee that there would be no interference with aliasing effects present after demodulation had to be ensured. After much investigation, it was found that the signal of interest in both the forward and reverse channels could be safely brought down to IF without any interference.

It was also discovered that the base station and the mobile phone would still communicate with each other when the signals were demodulated down to baseband before they were acquired by the FPGA. Because the ADCs are not guaranteed to function properly when acquiring signals below 1 MHz, it appeared that there would be a local fade in the channel, similar to the channel modeled by Mar and Chen [19].

Finally, non-uniform sampling was implemented as a low complexity method of injecting noise. Three separate approaches were taken during the implementation. The first approach was a proof of concept to show that it was possible to introduce noise using non–uniform sampling. The other two approaches investigated a simple method of incrementally introducing noise.

# Chapter 2

# **Overview of Architecture**

## 2.1 Description of System

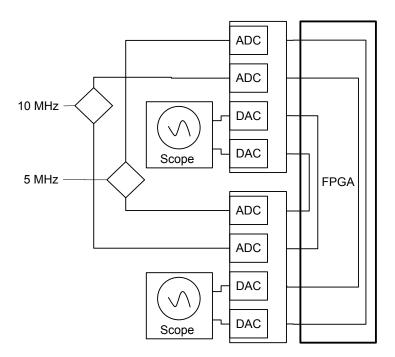

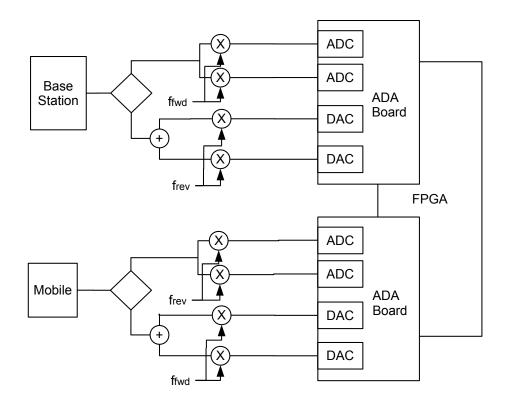

The system proposed is placed in-between a base station and a CDMA–enabled phone using the PCS1900 standard and handles all communication between the two. This is shown graphically in Figure 2.1. Since the 10 MHz wide I and Q signal components are separated before they are passed to the FPGA there is a minimum requirement of four ADCs and four DACs; two of each on both the sending and receiving side. Because the ADCs have a documented lower bound on the frequency they are able to acquire, an IF of 10 MHz will be used to transmit the individual I and Q channels from the demodulator to the ADCs.

Because the FPGA is the centre of the design, the architecture is able to be broken up into two separate sides: one side that includes the base station and another side that includes the mobile. Because of this split, it is possible to use the FPGA to

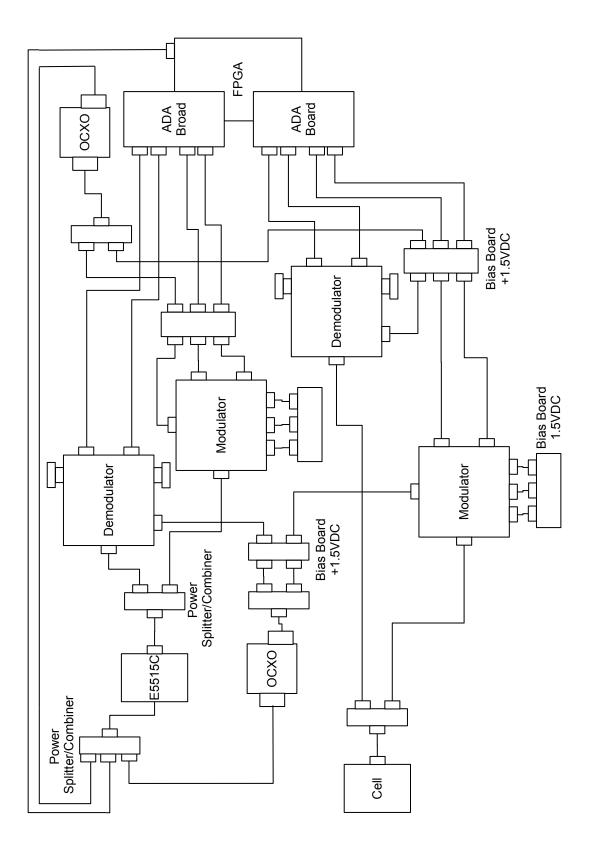

Figure 2.1: High–level proposal

control the communications path and monitor all data being passed back and forth.

For all except one test, the signals were not demodulated down to baseband but instead to an IF. This was done because of limitations of the ADCs, however, it also means that this architecture can be implemented in such a way that it does not impede on an individual user's privacy.

## 2.2 Overall Requirements Analysis

The major requirement of this project was to establish a communications channel through a medium that was externally controllable. External control could be done through a connection to a personal computer, or even a simple approach such as using pushbuttons and dip switches present on most FPGA evaluation boards. This transparent pass-through system would then be extensible to further assist researchers. In order to facilitate the extensibility, the system must also be reconfigurable so that new tests and algorithms can be implemented.

In order to achieve data pass-through, the system would have to appear transparent so that there is minimal data corruption and delay. The delay introduced by the system should be minimal. Because of this, the processing speed of the system must guarantee a timely response. This can be done by choosing fast components and using a parallel architecture.

Keeping the final implementation cost effective was also a requirement due to a limited budget.

### 2.2.1 Baseband Data Transfer Rate

Since the maximum RTAP rate for the EVDO protocol over the cdma2000 standard is 153.6 kbps for the reverse link and 2.4 Mbps for the forward link, the bus transporting the data must at a minimum support double the sum of these speeds.

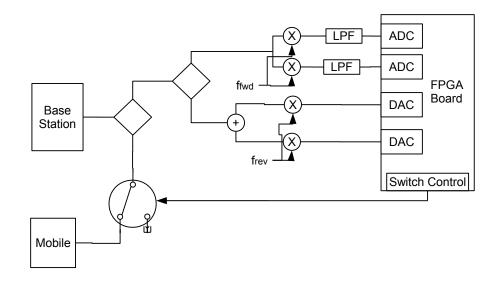

Figure 2.2: Initial design idea.

However, if the data is to be passed through at an IF, the bus has to ensure a throughput of double the IF to compensate for data at IF going in both directions. At the IF rate used, the GPIO pins provided by all the FPGAs investigated for this project were able to transfer data at the necessary speeds.

### 2.3 Architecture Design Iterations

The design of the overall system went through many iterations. Some changes occurred because they made the design more extensible, other changes were made because of the difficulty and cost of procuring parts. Major decisions are discussed below.

### 2.3.1 Initial Designs

Shown in Figure 2.2, the initial design had some major issues that needed to be resolved. Top among them is that the FPGA has to generate the data required for the test, or at least be able to play back a pre-recorded data stream for testing.

Figure 2.3: Functional diagram for the final design.

A switch was to be included so that the mobile would be taken completely out of the loop, and the entire data transfer would be supported by the architecture that was to be designed. Since implementing the EVDO standard would have been a task too large given the time constraints, and the playback of recorded data would have not guaranteed the normal responses to various channel perturbations, these ideas were eventually rejected.

Another design iteration was similar to the first, however, it required a relatively expensive and difficult–to–obtain diplexer, and still required that the entire CDMA/EVDO specification be implemented in the FPGA. Such an implementation would have increased the time to completion to an unreasonable length.

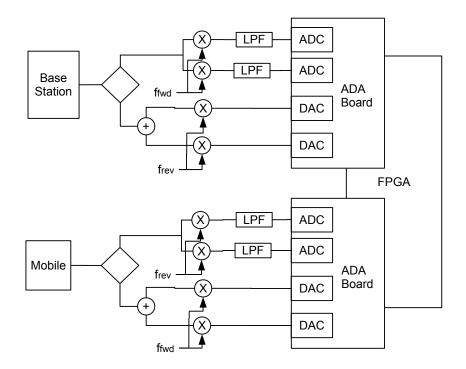

### 2.3.2 Final Idea

The final functional design which was built is shown in Figure 2.3. This design has the benefit of not needing the redundant diplexer, has fewer power splitter/com-

biners, and allows for both the forward and reverse links to be completely separated, as well as also having the I and Q channels separated on each link. The trade-off, however, is a slightly higher cost for the FPGA system. However, cost was kept down by choosing the Terasic<sup>®</sup> DE3 FPGA development board which had the resources to attach two ADA daughter boards. This is discussed further in Chapter 3.

# Chapter 3

# Hardware Selection

In order to meet the requirement of being cost effective, the majority of the system proposed was implemented using COTS components. In doing so, this removed the need to design complex PCBs and allowed the focus to be shifted to unit testing and full system tests. Although one PCB was required to be designed, it was relatively simple compared to the Altera<sup>®</sup> DE-3 [9] development board used.

One of the first major decisions made while selecting hardware was choosing between a microprocessor-based design, or an FPGA-based design. Because the I and Q channels need to be captured and processed simultaneously, having the ability to perform parallel processing became a requirement. Also, if a general purpose central processing unit were implemented, the time it would take to perform any signal processing would become an issue. Although both platforms would provide an extendable architecture, the choice to use an FPGA was ultimately made because of it's high reconfigurability to perform specific tasks.

## 3.1 Clock Sources

Several clock sources were investigated because of the requirement to have a highly stable reference frequency. Standard clock sources which were based on rubidium oscillators, cesium oscillators, the GPS reference signal and the CDMA reference signal were investigated, before the decision to purchase two high stability OCXO-based signal sources was made. Unlike the other options, this provided a stable 10 MHz reference output out of the back panel which could be used to drive other parts of the project to keep everything locked together, and did not require any custom PCBs to be built to provide the high frequency clock sources required for modulation and demodulation.

### 3.2 Individual Part Requirements

### **3.2.1** Modulators and Demodulators

The Hittite<sup>®</sup> HMC97LP4 modulators and Hittite<sup>®</sup> HMC597LP4 demodulators are used in this project. The demodulators were required to bring signals from the PCS band, in the 1900 MHz range, down to an IF which could be acquired by the FPGA. The modulators are required to do the opposite, bring signals from the IF up to the appropriate PCS band. Although the PCS band is used for the purposes of this project, the modulator's output and demodulator's input have an operational range of 100-4000 MHz [10][11]. This allows the system put forward to operate over a large range, and can be used in the future to run tests in another frequency band.

### **3.2.2** FPGA and Daughter Cards

Most FPGA development boards investigated included ADCs and DACs prebuilt on to them. However, all of the development boards investigated contained only one or two ADCs and DACs each, if any. If the board did not contain enough ADCs and DACs, the ability to network the FPGAs together would become a requirement. Another possible solution to this problem, and ultimately the solution chosen for this project, was to use a board which was extendable in such a way that daughter cards which contained the required four ADCs and four DACs could be used. Because all of this was contained on one FPGA board, synchronization between the ADA boards was made trivial, and allowed for data to be passed through the system at rates much higher than needed. Also, not having to create a communication interface for two FPGAs simplified the final design.

Because an IF of 10 MHz was selected, the ADCs and DACs chosen would have to ensure at least a minimum of a 40 MHz sampling rate in order to satisfy the Nyquist criterion; bandpass sampling requires the sampling frequency is more than four times the width of the passband. On both sides of the FPGA the signals are broken into their I and Q components, and then passed into the FPGA. After any signal processing has taken place, the I and Q components are transmitted out of the FPGA, recombined and continue along the communications channel.

### 3.3 System Power Requirements

When supplied by a 5  $V_{DC}$  source, the maximum given current requirement of the demodulator is 230 mA, and 168 mA for the modulator. Since there are two modulators and two demodulators, the total power required is 796 mA. The bias–Ts discussed in Section 4.2 are also powered by the 5  $V_{DC}$  power supply, however their current requirement is negligible.

The amplifier is powered by a separate  $12 V_{DC}$  PSU as indicated in the part specifications. The FPGA board included its own power supply, and only required a 120 V outlet.

### 3.4 Amplifiers

To help with signal demodulation, a connectorized amplifier was included in the final design in an effort to boost the signal of interest. This was done as an attempt to utilize more of the ADCs dynamic range. Had the amplifiers been excluded, the ADCs' resolution would have been reduced. The amplifier used was a wide bandwidth, low noise Mini-Circuits<sup>®</sup> ZX60-6013E-S+. At a frequency of 2000 MHz, the gain is 15.2 dB.

# Chapter 4

# Implementation

## 4.1 Selected Parts

#### 4.1.1 FPGA Development Board

At the centre of this system is an Altera<sup>®</sup> DE–3 development board which includes the Stratix III<sup>®</sup> FPGA, and two Terasic<sup>®</sup> ADA boards [12]. The ADA boards are where the ADCs and DACs reside. On both sides of the FPGA the signal is broken into its I and Q components, and then passed into the FPGA. After any signal processing has taken place, the signal is transmitted out of the FPGA, recombined and continues along the communications channel.

The ADCs have a maximum sampling rate of 65 MHz [13], and the DACs have a maximum update rate of 125 MHz [14]. This met the requirements with a wide margin.

### 4.1.2 Modulators and Demodulators

The Hittite<sup>®</sup> modulators were purchased on a connectorized board to minimize the time required for setup. The modulator used was intended to be driven by a dual– ended signal with a 1.5  $V_{DC}$  offset on both ends. However, for this project, only a single–ended signal was required and applied; the negative side of the terminal was not used, but instead terminated. It is important to note that without the 1.5  $V_{DC}$  offset in the signal voltage on the positive terminal as well as the constant 1.5  $V_{DC}$  present at the negative terminal, the modulator would not operate.

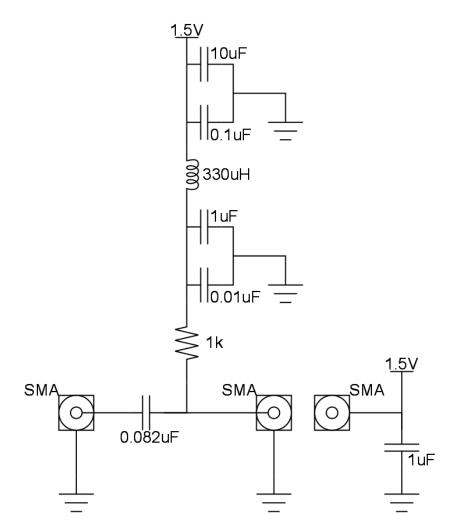

The chosen demodulator was also from Hittite<sup>®</sup>. It was selected because of implementation knowledge that already existed, expediting implementation and testing. The demodulator only required that the local oscillator be offset by  $1.5 V_{DC}$ . This was taken account of when designing the bias board shown in Appendix A.1 and described below.

### 4.2 Bias Board

Because the modulators and demodulators required that certain input ports include a  $1.5V_{DC}$  offset, a bias board was designed and constructed. The PCB in Figure 4.1 is the signal biasing board which was designed and implemented. It consists of a simple bias–T circuit. It was designed with both the modulators and demodulators in mind; only the needed sections of each board were populated. Each connectorized side of the bias board had a signal input, a signal output, and a 1.5 V<sub>DC</sub> output. The signal output was the small signal input transposed +1.5 V<sub>DC</sub>.

Spice simulations were run to ensure proper operation in the 1900 MHz range. The circuit diagram of the bias–T circuit can be seen in Appendix A.1. The 1.5  $V_{DC}$  supplied to the circuit was provided by a voltage regulator that was built onto the board. The board is powered by a 5  $V_{DC}$  power source.

The decision to use an external 5  $V_{DC}$  power source was made so that a common power supply unit could be used for almost all parts on the board: both the modulators and the demodulators also require a 5  $V_{DC}$  power supply. Since the current requirements described in Section 3.3 show that the current draw was not large,

Figure 4.1: Signal biasing board.

all parts that required 5  $V_{DC}$  were able to be powered using a single supply.

### 4.3 Frequency Selection

For the investigation of frequencies to be used for the local oscillator of the modulators and demodulators, a MATLAB<sup>®</sup> program was written for simulating the artifact interference caused during the modulation and demodulation phases.

The final proposed design, shown in Figure 2.3, called for a LPF to remove any signals outside of the acquisition range. Originally, the filter was to remove any of the sampling artifacts that may be caused. After modeling the acquisition in MATLAB<sup>®</sup>, it was discovered that the signal could be cleanly acquired without any sampling artifacts caused by harmonics. The final implemented design can be seen in Figure C.1.

A sampling frequency of  $f_s = 62.5$  MHz was used in conjunction with the reverse channel modulation and demodulation frequency  $f_r = 2007$  MHz, and the forward channel modulation and demodulation frequency  $f_f = 1930$  MHz. Other frequencies that were shown to have good performance were  $f_r = 1893$  MHz and  $f_f = 1993$  MHz. The MATLAB<sup>®</sup> code that was used to model this behaviour is shown in Appendix D. By selecting frequencies that would ensure that the signal of interest in both the forward and reverse communication channels were untouched by sampling artifacts and removing the LPF, it enabled this architecture to be a general purpose, protocol agnostic, channel interception and modification design. With this, it becomes possible to extend the use of this project past the CDMA/EVDO research to study other standards.

### 4.4 Clock Synchronization

Supplying a base band signal to the Hittite<sup>®</sup> modulators and demodulators are two high–stability OCXO clock sources. To avoid any synchronization issues, the clock sources, FPGA and base station were locked to a common 10 MHz reference signal supplied by one of the OCXO clock sources.

## 4.5 **RF** Isolation

To isolate the mobile from any other corporate network that is being used, and to ensure that the implemented system did not interfere with any legitimate businesses, the mobile was placed inside a metal anechoic chamber. It was found that an empty chamber caused the mobile to not connect, and it was postulated that there were too many RF reflections on the inside of the chamber. Special absorptive RF insulation barriers were added to the chamber to reduce the interior reflections. Also, holes that were present in the chamber were discovered and were sealed using metal tape. A special cable and adapter which plugged into the back of the mobile and bypassed its antenna was purchased in an attempt to have a more managable size system. This provided limited success, as the mobile was not purchased new and the antenna bypass was suspected of having an intermittent connection. For all tests performed for this thesis, the anechoic chamber was used.

# Chapter 5

# Testing

Throughout the development of this architecture, testing had been considered of paramount importance. In Harriman's thesis [15] it was found that the parts selected did not always conform to their associated specification sheet. Because this project and Harriman's shared a few common parts, it was important to ensure proper testing was done at every stage.

## 5.1 Bias Boards

A prototype board was first commissioned, thoroughly tested, and performed as expected with no errors or unexpected behaviours present. Testing was conducted using a signal source and an oscilloscope. A signal was presented at the input port, and the oscilloscope which was connected to the output port displayed a signal identical to the input with the required  $V_{DC}$  offset.

## 5.2 Modulator

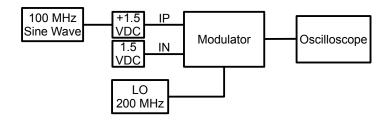

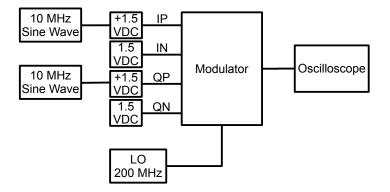

The initial tests of the modulator were done using the system layout in Figure 5.1. Testing both the I and Q channels were done on the setup shown in Figure 5.2.

Figure 5.1: Test setup for testing the Inphase.

Figure 5.2: Test setup for fully testing the modulator.

A mathematical model was used to show the expected output as seen by the oscilloscope, and was extended later to include the expected output when both the I and Q channels were used.

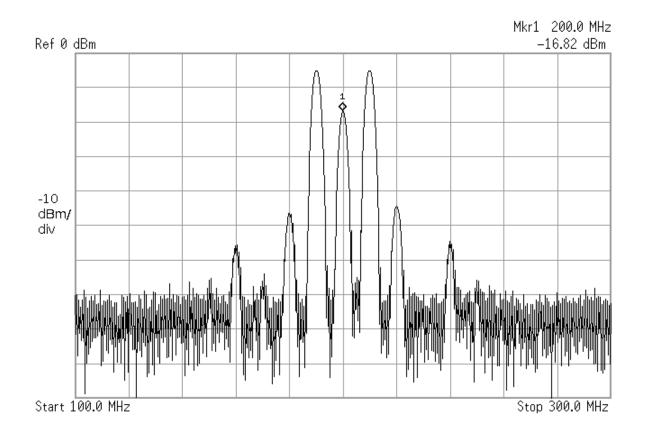

The spectral output is shown in Figure 5.3 from the tests done using the setup in Figure 5.2, which matched expectations.

### 5.3 Demodulator

Testing of the demodulator required that the modulator first be successfully implemented. Once the modulator was successfully implemented, the output of the modulator was connected to the input of the demodulator. Using the same clock source for the demodulator as the modulator, it was possible to recover the original signals that were fed into the modulator. This was verified for both the I and Q

Figure 5.3: Spectral output from the modulator.

Figure 5.4: FPGA test setup.

channels independently, and finally concurrently. The power level received was not exactly matched to the power transmitted, but some loss was expected. This could be attributed to using the demodulators in single–ended mode, which was found to cause a small amount of power loss.

## 5.4 FPGA

Several tests were conducted on the FPGA and ADA daughter boards to ensure proper operation. Each test built on the previous one, until the test setup shown in Figure 5.4 was reached. Using this setup, it is possible to show that the signal captured on any ADC channel was able to be regenerated using the DAC channel on the opposite board. This setup closely relates to the final setup that was used in the final implementation.

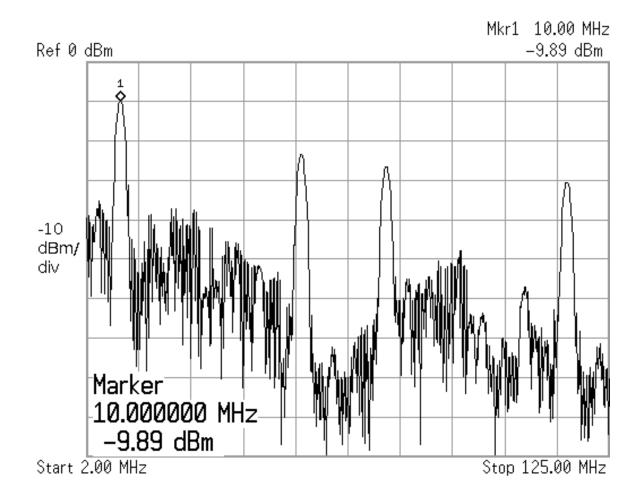

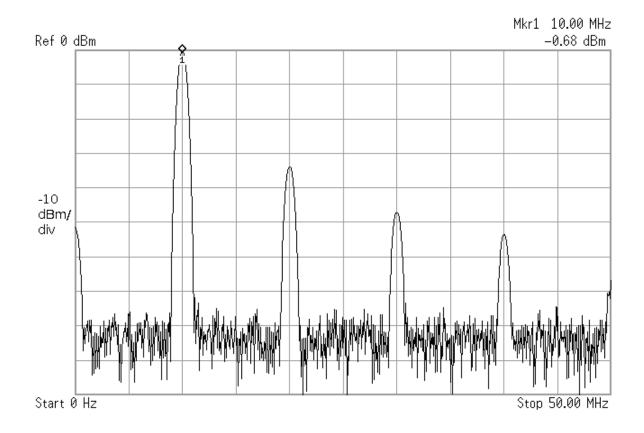

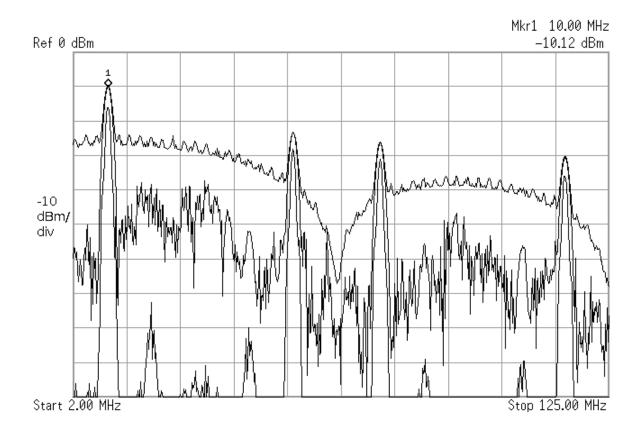

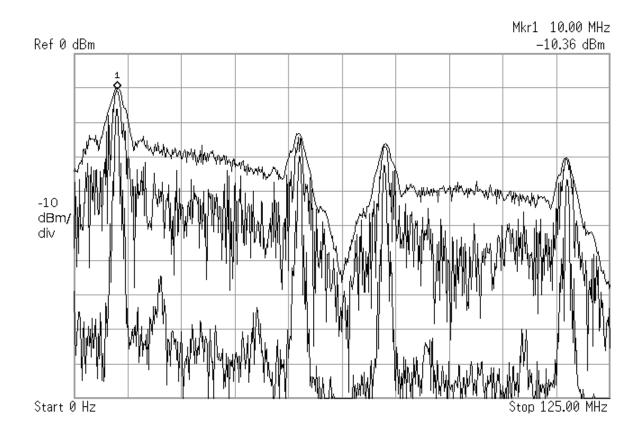

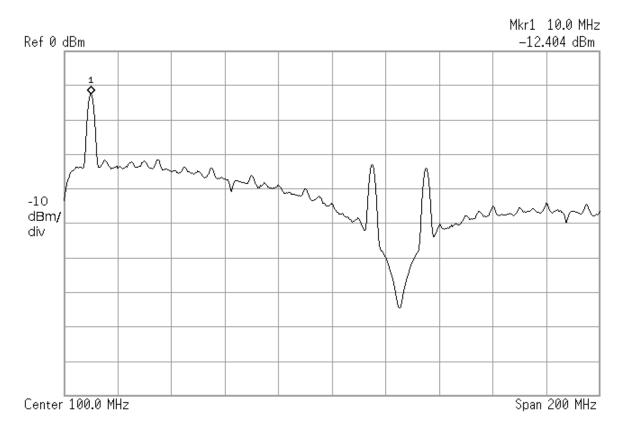

A 10 MHz sinusoidal signal was fed into an ADC port on the FPGA at 0 dBm,

Figure 5.5: Resulting spectrum of a 10 MHz signal passing through the FPGA.

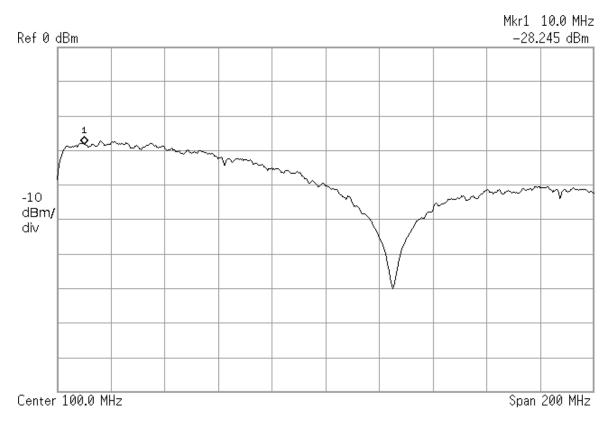

sampled and regenerated at 62.5 Msps, then fed directly into a spectrum analyzer. The resulting frequency graph shown in Figure 5.5 is a waveform capture showing the output signal is approximately 10 dBm below the input signal.

Also shown in Figure 5.5 is that the noise floor has been increased. For reference, see Figure 5.6, which shows the 10 MHz sine wave that was output from the signal source and fed directly into the spectrum analyzer. The extra spikes in Figure 5.5 that are above the expected 10 MHz signal are artifacts that occur because of the sampling performed by the ADCs.

Figure 5.6: A 10 MHz input signal directly from the clock source used without passing through the architecture.

Figure 5.7: Data being transmitted during an FTAP test through the system.

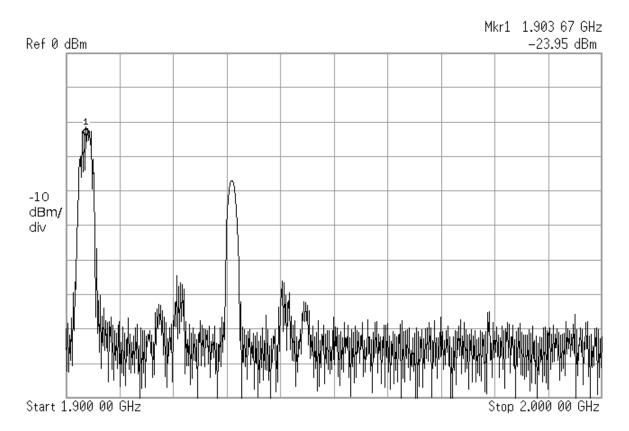

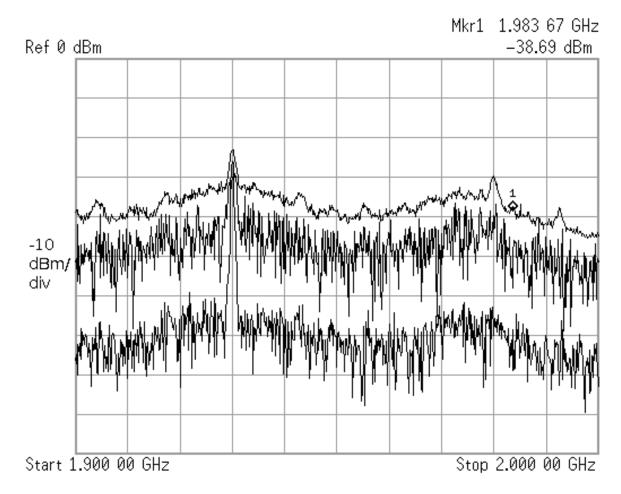

## 5.5 CDMA/EVDO Transparency

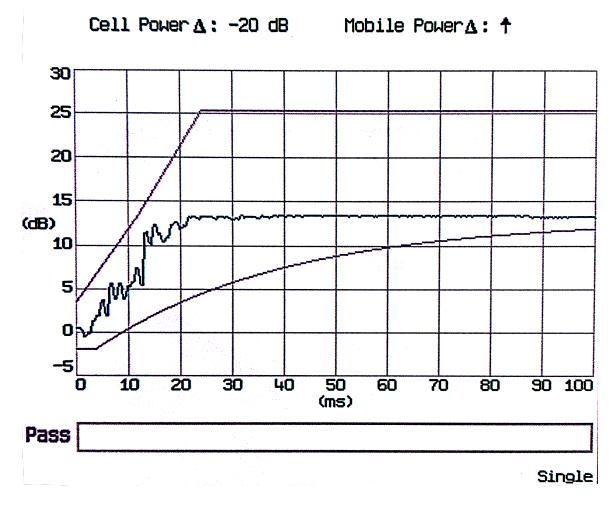

To show that the system was able to appear transparent to both the mobile and the base station, tests were conducted showing that data was able to be transmitted and received. This was done by using a power splitter/combiner between the FPGA and the mobile phone and allowing a spectrum analyzer to observe the transactions taking place. Figure 5.7 is a spectral plot showing the data being sent from the mobile to the base station at 1903.75 MHz; marker 1 is positioned at the channel in use. The other obvious peak at 1930 MHz in Figure 5.7 is a result of the modulation that was performed to transpose the signal from IF to the required 1903.75 MHz.

Figure 5.8 shows that the system put forward is successfully able to pass through commands from the base station to the mobile regarding power–control. The top and bottom lines are power limits which move in time. The middle line is the actual power output. The test shown was a "power-up" command: the base station signaled the mobile to increase the cell power by 20 dBm. As can be seen in the Figure, the mobile passed the test, showing that the system in place between the mobile and the base station did not adversely affect the communication between the two.

Figure 5.8: A successful power-control test.

## Chapter 6

## **Non-Uniform Sampling**

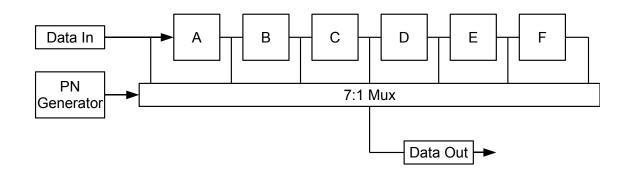

The ability to implement non-uniform sampling on this project was in no small part because of the reconfigurable nature of the architecture; having easy access to both the forward and reverse channels allowed for new manipulations within the FPGA. To implement non–uniform sampling, the uniformly sampled signal was fed from the ADC into a shift register, and a PN generator was used to select which register the output should be tied to. Because the goal was non–uniform sampling, the register selection needed to be random. The randomization was accomplished by implementing PN generator to select which register in the shift register was to be used for output. This has the effect of randomizing the sampling, and also does not guarantee sample order.

Randomization caused by implementing this style of non-uniform sampling is analogous to multipath effects—delays caused in time and noise generated by the signal not arriving in the correct order due to various reflective surfaces in the environment. In this implementation, the clock for the PN generator is much higher than the signal frequency, and the number of buffers were chosen to ensure that samples were being taken within a confined region of the signal period.

#### 6.1 Mathematical Model

In an effort to model the expected variance of non–uniform sampling, mathematical analysis was done. Starting with a sinusoidal signal s(t) described in equation 6.1,

$$s(t) = \cos(2\pi f_1 t) \tag{6.1}$$

where  $f_1$  is the frequency of the signal, and t represents time. For uniform sampling, all samples are taken at equal discrete intervals shown in equations 6.2 and 6.3,

$$s_n = s(t)|_{t=nT} \tag{6.2}$$

$$=\cos(2\pi f_1 nT) \tag{6.3}$$

where n is the index number, T is the time between samples, and  $s_n$  is the indexed discrete signal. However, in non–uniform sampling the discrete intervals that the samples are taken at are not equally spaced leading to the equation

$$V_n = s(t)|_{t=nT+\Delta n}$$

= cos(2\pi f\_1(nT + \Delta n))

= cos(2\pi f\_1nT + 2\pi f\_1\Delta n) (6.4)

$V_n$  is the indexed discrete non–uniformly sampled signal, and  $\Delta n$  is the difference in n. To demonstrate non–uniform sampling, an input signal of  $y = \cos(\theta)$  was used where  $\theta$  is distributed as a uniform continuous random variable in the range  $0 \to \pi$ . Also,  $\Delta$  is distributed as a normal random variable with the range of  $0 \to \sigma_n^2$ , where  $\sigma_n^2$  is the variance. These are described in equations 6.5 and 6.6.

$$\theta_1 \sim U(0,\pi) \tag{6.5}$$

$$\Delta \sim N(0, \sigma_n^2) \tag{6.6}$$

Given Y in equation 6.7,

$$Y = \cos(\theta) \tag{6.7}$$

equations 6.5 and 6.6 can be inserted into 6.7 to get equation 6.8.

$$Y = \cos(\theta_1 + \Delta) \tag{6.8}$$

The formula to find the variance of the non-uniformly sampled signal is shown in equation 6.9.

$$\sigma_Y^2 = E[Y^2] - E^2[Y] \tag{6.9}$$

Starting with the variance in equation 6.10, equations 6.5 and 6.6 are inserted to obtain equation 6.11, which leads to equation 6.12.

$$E_{\theta_1,\Delta}[Y^2] = \iint_{-\infty}^{+\infty} g(x) f_{x,y}(x,y) dx dy$$

(6.10)

$$= \iint_{-\infty}^{+\infty} \cos^2(\theta_1 + \delta) f_{\theta_1,\Delta}(\theta_1, \delta) d\theta_1 d\delta$$

(6.11)

$$= \iint_{-\infty}^{+\infty} \cos^2(\theta_1 + \delta) f_{\Theta_1}(\theta_1) f_{\Delta}(\delta) d\theta_1 d\delta$$

(6.12)

The range of equations 6.5 and 6.6 are then used when determining what range the integrals will cover and also inserted into equation 6.12 which is shown in equation 6.13, which leads to equation 6.14.

$$E[Y^2] = \int_{-\infty}^{+\infty} \int_0^{\pi} \cos^2(\theta_1 + \sigma) \left(\frac{1}{\pi}\right) \left(\frac{1}{\sqrt{2\pi\sigma_n}} e^{-\frac{\delta^2}{2\sigma_n^2}}\right) d\theta_1 d\delta \tag{6.13}$$

$$= \frac{1}{\pi} \int_{-\infty}^{+\infty} \frac{1}{\sqrt{2\pi\sigma_n}} e^{-\frac{\delta^2}{2\sigma_n^2}} \left( \int_0^{\pi} \cos(\delta + \theta_1) d\theta_1 \right) d\delta$$

(6.14)

To solve equation 6.14, a cos integration identity is used. It is shown in equation 6.15.

$$\int \cos(a+x)dx = \frac{a+x}{2} + \frac{1}{4}\sin(2(a+x))$$

(6.15)

Using equation 6.15 it is possible to continue solving equation 6.12 to get equation 6.16.

$$E[Y^{2}] = \int_{-\infty}^{+\infty} \frac{1}{\sqrt{2\pi\sigma_{n}}} e^{-\frac{\delta^{2}}{2\sigma_{n}^{2}}} \left(\frac{\delta+\theta_{1}}{2} + \frac{1}{4}(\sin(\delta+\theta_{1}))\right) \Big|_{\theta_{1}=0}^{\pi} d\delta$$

(6.16)

Solving the inner part of equation 6.16 produces equation 6.17.

$$\frac{\delta + \theta_1}{2} + \frac{1}{4} (\sin(\delta + \theta_1)) \Big|_{\theta_1 = 0}^{\pi}$$

$$= \frac{\delta + \pi}{2} + \frac{1}{4} \sin(2\delta + 2\pi) - \left[\frac{\delta}{2} + \frac{1}{4}\sin(2\delta)\right]$$

$$= \frac{\pi}{2} + \frac{1}{4} \left[\sin(2\delta + 2\pi) - \sin(2\delta)\right]$$

$$\therefore \sin(2\delta + 2\pi) = \sin(2\delta)$$

$$\therefore = \frac{\pi}{2} + \frac{1}{4} \left[\sin(2\delta) - \sin(2\delta)\right]$$

$$= \frac{\pi}{2}$$

(6.17)

Inserting equation 6.17 into equation 6.16, produces equation 6.18.

$$E[Y^{2}] = \frac{1}{\pi} \int_{-\infty}^{+\infty} \frac{1}{\sqrt{2\pi}\sigma_{n}} e^{-\frac{\delta^{2}}{2\sigma_{n}^{2}}} \left(\frac{\pi}{2}\right) d\delta$$

$$= \frac{1}{\pi} \frac{\pi}{2} \frac{1}{\sqrt{2\pi}\sigma_{n}} \int_{-\infty}^{+\infty} e^{-\frac{\delta^{2}}{2\sigma_{n}^{2}}} d\delta$$

$$= \frac{1}{2\sqrt{2\pi}\sigma_{n}} \left[ \sqrt{\frac{\pi}{2}} \sigma_{n} \operatorname{erf}\left(\frac{\delta}{2\sigma_{n}}\right) \right] \Big|_{\delta=-\infty}^{+\infty}$$

(6.18)

The integration in equation 6.19 was used in equation 6.18.

$$\int e^{-\frac{\delta^2}{2\sigma_n^2}} d\sigma = \left[ \sqrt{\frac{\pi}{2}} \sigma_n \operatorname{erf}\left(\frac{\delta}{2\sigma_n}\right) \right]$$

(6.19)

Variable substitution is performed, shown in equation 6.20.

$$x = \frac{\delta}{2\sigma_n} \tag{6.20}$$

and is used in solving equation 6.18, which is continued in equation 6.21

$$E[Y^{2}] = \frac{1}{2\sqrt{2\pi}\sigma_{n}} \left[ \sqrt{\frac{\pi}{2}}\sigma_{n} \left( \lim_{x \to \infty} \operatorname{erf}(x) - \lim_{x \to \infty} \operatorname{erf}(-x) \right) \right]$$

$$= \frac{1}{2\sqrt{2\pi}\sigma_{n}} \left[ \sqrt{\frac{\pi}{2}}\sigma_{n} \left( 1 - (-1) \right) \right]$$

$$= \frac{1}{2\sqrt{2\pi}\sigma_{n}} \left[ 2\sqrt{\frac{\pi}{2}}\sigma_{n} \right]$$

$$= \frac{\frac{\sqrt{\pi}}{\sqrt{2}}}{\sqrt{2}\sqrt{\pi}}$$

$$= \frac{1}{2}$$

(6.21)

Where  $\operatorname{erf}(x)$  is the error function of x. Now, solving the  $E^2[Y]$  term in equation 6.9 is shown below in equation 6.22.

$$\begin{aligned} E_{\theta,\Delta} &= \iint \cos(\theta_1 + \delta) f_{\Theta}(\theta_1) f_{\Delta}(\delta) d\theta_1 d\delta \\ &= \iint \cos(\theta_1 + \delta) \left(\frac{1}{\pi}\right) \left(\frac{1}{\sqrt{2\pi\sigma_n}} e^{-\frac{\delta^2}{2\sigma)n^2}}\right) d\theta_1 d\delta \\ &= \frac{1}{\pi} \int_{-\infty}^{+\infty} \frac{1}{\sqrt{2\pi\sigma_n}} e^{-\frac{\delta^2}{2\sigma_n^2}} \int_{\theta_1=0}^{\theta_1=\pi} \cos(\theta_1 + \delta) d\theta_1 d\delta \\ &= \frac{1}{\pi} \int_{-\infty}^{+\infty} \frac{1}{\sqrt{2\pi\sigma_n}} e^{-\frac{\delta^2}{2\sigma_n^2}} \left[\sin(\theta_1 + \delta)\right] \Big|_{\theta_1=0}^{\pi} d\delta \\ &= \frac{1}{\pi} \int_{-\infty}^{+\infty} \frac{1}{\sqrt{2\pi\sigma_n}} e^{-\frac{\delta^2}{2\sigma_n^2}} \left[\sin(\delta - \pi) - \sin(\delta)\right] d\delta \\ &= \frac{1}{\pi} \int_{-\infty}^{+\infty} \frac{1}{\sqrt{2\pi\sigma_n}} e^{-\frac{\delta^2}{2\sigma_n^2}} \left[-2\sin(\delta)\right] d\delta \\ &= -\frac{2}{\pi} \int_{-\infty}^{+\infty} \frac{1}{\sqrt{2\pi\sigma_n}} e^{-\frac{\delta^2}{2\sigma_n^2}} \sin(\delta) d\delta \\ &= -\frac{2}{\pi\sqrt{2\pi\sigma_n}} \left[-\frac{1}{2} e^{-\frac{\sigma_n^2}{2}} \sqrt{\frac{\pi}{2}} \sigma_n \left(\operatorname{erfi}\left(\frac{\sigma_n^2 - i\delta}{\sqrt{2\sigma_n}}\right) + \operatorname{erfi}\left(\frac{\sigma_n^2 + i\delta}{\sqrt{2\sigma_n}}\right)\right)\right] \Big|_{\delta=-\infty}^{+\infty} \end{aligned}$$

(6.22)

The erfi(x) used in equation 6.22 is the imaginary error function of x, and is defined in equation 6.23. As  $\delta \to \infty$ , the other terms inside the erfi(x) function in equation 6.22 do not affect the term that is tending toward infinity, they can be considered insignificant in this case.

$$\operatorname{erfi}(x) \equiv -i\operatorname{erf}(ix)$$

(6.23)

The erfi(x) function has the following properties:

$$\lim_{x \to \infty} \operatorname{erfi}(x) = \infty$$

$$\lim_{x \to \infty} \operatorname{erfi}(-x) = -\infty$$

$$\lim_{x \to \infty} \operatorname{erfi}(ix) = i$$

$$\lim_{x \to \infty} \operatorname{erfi}(-ix) = -i$$

Using the last two properties, equation 6.22 becomes

$$E_{\theta,\Delta} = -\frac{2}{\pi\sqrt{2\pi}\sigma_n} \left[ -\frac{1}{2}e^{-\frac{\sigma_n^2}{2}}\sqrt{\frac{\pi}{2}}\sigma_n(0) \right]$$

= 0 (6.24)

Inserting the results from equation 6.18 and equation 6.24 into the variance equation 6.9, gives equation 6.25.

$$\sigma_Y^2 = E_{\theta_1,\delta}[Y^2] - E_{\theta_1,\delta}^2[Y] = \frac{1}{2} - 0$$

$$= \frac{1}{2}$$

(6.25)

For this test case with a sinusoidal wave of unity amplitude, the variance in the readings will be half. This makes sense, as the distribution used for this mathematical model was normalized, as well as the randomness of the intervals between readings was uniformly distributed. This result means that if readings are taken using non-uniform sampling, and no effort is put in to compensate for the varying time intervals, there will be noise present. As stated, this derivation shows the variance present will be half of the signal introduced.

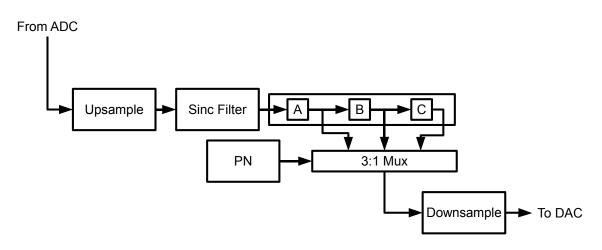

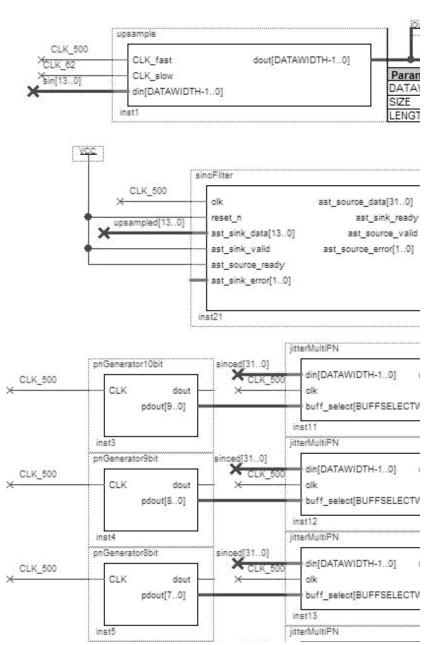

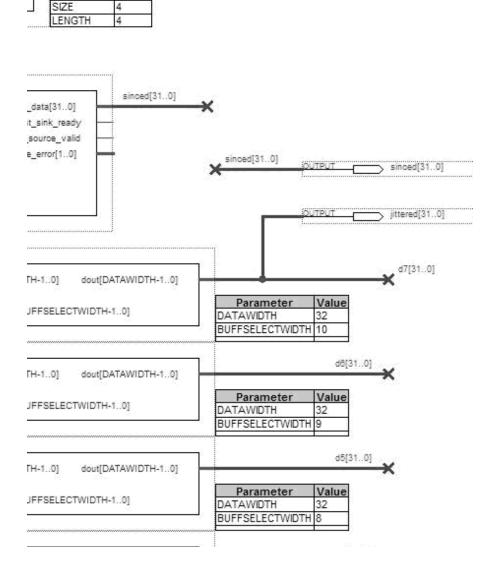

Figure 6.1: Non-uniform sampling implementation.

#### 6.2 Implementation

The non-uniform sampling was implemented using a type of shift register system seen in Figure 6.1. The input was captured by the ADC and appeared as din. When new data was introduced, the initial value was shifted into the shift register and the new data appeared as din.

Using a linear recursive sequence generator with the equation  $P(x) = x^5 + x^2 + 1$ to implement a PN generator, registers were chosen at random and their outputs were connected to the module outputs. Because P(x) is a primitive prime polynomial, the maximum sequence length of 31 states was achieved. The rate at which registers were chosen is controlled by the clock that the PN generator uses to advance its own internal registers. A relationship appeared between aliasing in the noise and the clock speed. When the clock was set to choose a different register at 125 MHz, there were double peaks around every 2.016 MHz. However, while running the PN generator clock at a higher frequency—at 200 MHz—there are only single peaks with less separation. A possible explanation to this phenomenon is the period that the PN sequence repeats. At 125 MHz, P(x) repeated every 248 ns, while running at 200 MHz it repeated every 155 ns.

The noise introduced using this method was noted as appearing as an ordered noise; there appear to be many aliasing effects at discrete intervals.

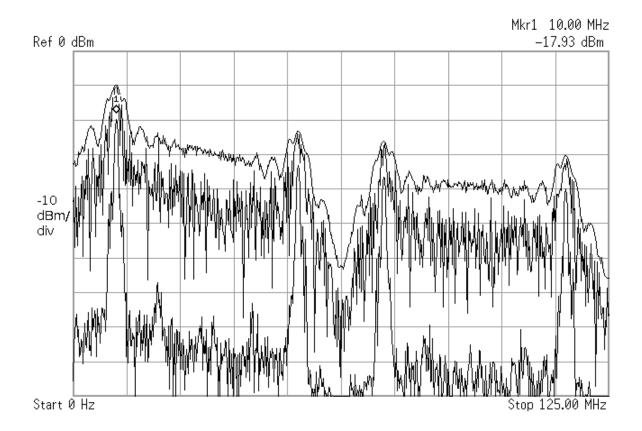

Figure 6.2: Showing the maximum value (top line), an instantaneous reading (middle line), and the minimum value (bottom line) of a 10 MHz signal using uniform sampling.

#### 6.3 Known Signal Tests

To show the noise that is introduced, a 10 MHz sine wave was used as an input signal. From there, various non-uniform sampling parameters were used. For reference, Figure 6.2 shows the output of the 10 MHz signal that was sampled uniformly through the FPGA. The tests were performed by applying the sine wave to the ADC input, processing the signal in the FPGA, outputting the result using a DAC, which is hooked directly to a spectrum analyzer for observation.

Input signals are sampled at 62.5 MHz by the ADCs, and output at 62.5 MHz by the DACs. During the up–sampling that was performed internally in the FPGA in this test, the signal was not zero padded, but repeated by reading the ADC output register multiple times before a new reading was taken. This causes the signal to be

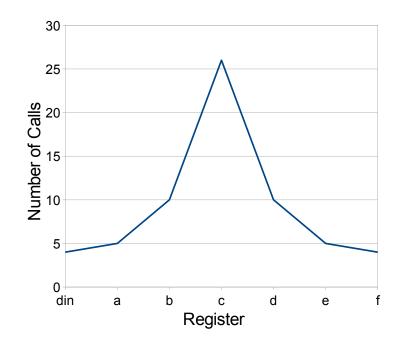

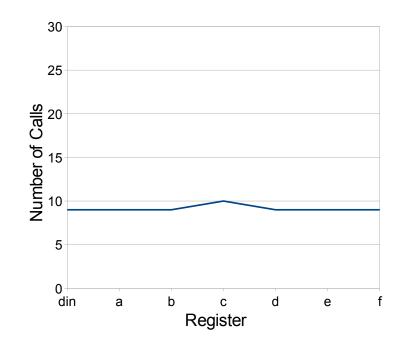

Figure 6.3: A normal distribution showing how many times each register is called per period.

repeated in the frequency domain above 62.5 MHz. Because these secondary signals are so far out of band, they do not interfere with the tests that are being performed at 10 MHz. The signal was then downsampled at the outputs by the DACs.

#### 6.3.1 Test Results

Once non-uniform sampling was applied more noise was obviously present in the system. For the first test, a PN generator with a normal distribution was used. The module as implemented takes the input from all the registers in a normalized distribution; the centre buffer gets chosen the majority of the time, while the far end buffers get chosen significantly less. This can be seen in Figure 6.3, where **din** is the input register, and the following registers are lettered in alphabetical order.

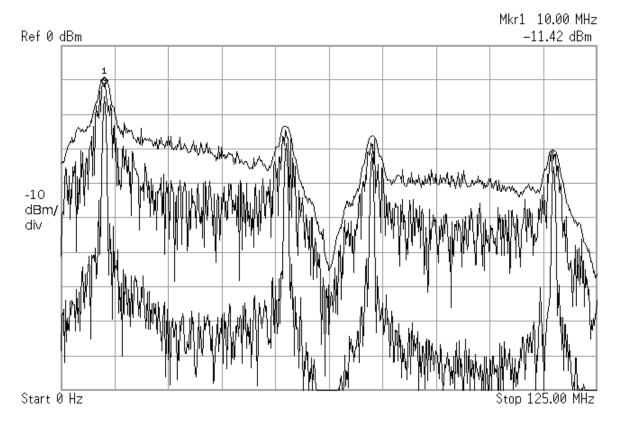

As can be seen in Figure 6.4, the maximum level noise has risen approximately 5 dBm near the 10 MHz range. The minimum noise has also risen 30 dBm around 10 MHz. The instantaneous reading of the signal has also risen. Also of note is the

Figure 6.4: Showing the maximum value (top line), an instantaneous reading (middle line), and the minimum value (bottom line) of a 10 MHz signal using non-uniform sampling.

peak at 10 MHz is less pronounced and has slightly increased width. The 10 MHz signal is approximately -10 dBm in both the uniform and non-uniform sampled cases. The input signal used was at 0 dBm; the -10 dBm discrepancy was mentioned earlier and is consistent with results found earlier.

For the next test, the distribution was modified so that the middle register in the shift array was called more often than during the first test, and the others less. This distribution is shown in Figure 6.5

The resulting spectrum is shown in Figure 6.6. There is almost no discernable difference between the modified distribution and the initial distribution.

Finally, a nearly evenly distributed selection algorithm was used, and is shown in Figure 6.7.

Figure 6.5: Modified distribution.

As can be seen again in Figure 6.8, there is no obvious difference between the even distribution and the previous two normalized distributions.

#### 6.3.2 Discussion

This implementation does not guarantee order is preserved when the output is connected to another buffer in the shift register. This could be the reason why the output signals seem to all have similar amounts of noise present. As mentioned earlier, the rate at which the output connection is changed seems to have more of an effect on the output signal.

In each of the three non-uniform sampling tests performed using a 10 MHz sine wave input signal the minimum value, or noise floor, was also increased. Looking only in the first half of the spectrum shown and excluding the second hump, the noise was increased to nearly a uniform value of about -70 dBm and varied by only 10 dBm, except near the null point at 62.5 MHz.

In observing the non-uniform sampling effects on the test signal, it can be seen

Figure 6.6: The resulting maximum value (top line), an instantaneous reading (middle line), and the minimum value (bottom line) of the spectrum using the modified normal distribution.

Figure 6.7: The nearly even distribution used for register selection.

Figure 6.8: The resulting maximum value (top line), an instantaneous reading (middle line), and the minimum value (bottom line) of the spectrum using the nearly even distribution.

that the maximum value of the spectrum (the top line in the Figures 6.4, 6.6, and 6.8) had only been slightly affected. The point at 10 MHz where the signal of interest resides has been widened in frequency, showing that noise is introduced around that area.

Simply stated, if there is no signal there will be no noise added, and where there is noise, the non-uniform sampling will add noise to that signal. Much research has been done and most of it appears to be focused on acquiring a signal and reproducing that signal free of noise, but also free of any harmonics. An example of this process is described by Brueller et al. where a mathematical model and an iterative estimation process is used to describe and recreate a signal [16]. Fares et al. showed a few methods of using non-uniform sampling and regenerating the signal using uniform methods [17]. That approach, however, requires that the order in which the signal is sampled be guaranteed. This was not the case in this test; instead of trying to clean the spectrum of noise, the goal was to introduce it. The notion of using non-uniform sampling and uniform sample generation to introduce noise in a specific channel in use is what sets this test apart from other literature.

#### 6.4 Application to Architecture

To establish a baseline, Figure 5.7 shows the communications channel of an FTAP test being performed and data being transfered. The first and highest peak shown is the channel being used, the second peak situated at approximately 1930 MHz is the frequency used by a clock source for modulation and demodulation.

During the tests using non-uniform sampling, the CDMA/EVDO system was not able to continue to transfer data, and resulted in all packets being lost, and eventually, the session between the phone and base station was also dropped. This indicates a limit to the amount of noise which can be introduced before failure. Shown

Figure 6.9: Noise dominating both forward and reverse channels.

in Figure 6.9 is the communications channel being dominated with noise during a non– uniform sampling test. The noise pattern is nearly identical for each of the 3 different non-uniform sampling scenarios used.

### 6.5 Noise Parameter Discovery

The previous tests implemented only non–uniform sampling with a signal generation rate equal to the signal acquisition rate. Also, the PN generator ran at a much higher rate from the rest of the system. The following is an attempt to specify which parameters could be modified to slowly introduce noise to the communication channel. For these tests, the input signal was acquired at 62.5 MHz and the output signal was generated at 125 MHz. Up–sampling to 250 MHz and downsampling to the output frequency of 125 MHz was performed internally in the FPGA. All modifications to the signal were performed at 250 MHz.

#### 6.5.1 Modification to PN Generator

The period of the PN generator was modified by using a higher order polynomial in the PN generator. This increased the maximum length sequence of which registers could be chosen; a smaller order polynomial used in the PN generator decreased the maximum length of the sequence.

Several PN generators were created; PN generators from 10th order down to 3rd order. The polynomials describing all PN generators used for testing are as follows [18]:

$$P(x) = x^{10} + x^3 + 1 ag{6.26}$$

$$P(x) = x^9 + x^4 + 1 \tag{6.27}$$

$$P(x) = x^8 + x^4 + x^3 + x^2 + 1$$

(6.28)

$$P(x) = x^7 + x + 1 \tag{6.29}$$

$$P(x) = x^6 + x + 1 \tag{6.30}$$

$$P(x) = x^5 + x^2 + 1 \tag{6.31}$$

$$P(x) = x^4 + x + 1 \tag{6.32}$$

$$P(x) = x^3 + x + 1 \tag{6.33}$$

Table 6.1 shows the length of each sequence. Primitive polynomials were chosen to ensure that the PN generator would have the maximum length sequence. This

| Table $0.1$ : | Length of sequences |

|---------------|---------------------|

| Equation      | Sequence Length     |

| 6.26          | 1023                |

| 6.27          | 511                 |

| 6.28          | 255                 |

| 6.29          | 127                 |

| 6.30          | 63                  |

| 6.31          | 31                  |

| 6.32          | 15                  |

| 6.33          | 7                   |

|               |                     |

Table 6.1: Length of sequences

was implemented in an effort to discover and isolate the parameter that affects the amount of noise introduced. For this a shorter shift register, consisting only of three registers, was introduced. Having all but two of the numbers supplied by the PN generator choose the middle register changed the distribution based on length of the PN sequence.

Figure 6.6 shows the basic design of the setup used for doing these tests. The incoming signal was upsampled by a factor of 4 and zero-padded, then passed through a  $\operatorname{sinc}(x)$  filter which interpolated and smoothed the upsampled signal before the data was put into the shift register. As data moved through the shift register, the PN generator selected which register to attach the output to. The PN generator was running at the same frequency as the incoming signal to the shift register. Downsampling by a factor of 2 was then performed to prepare the signal for generation by the DACs.

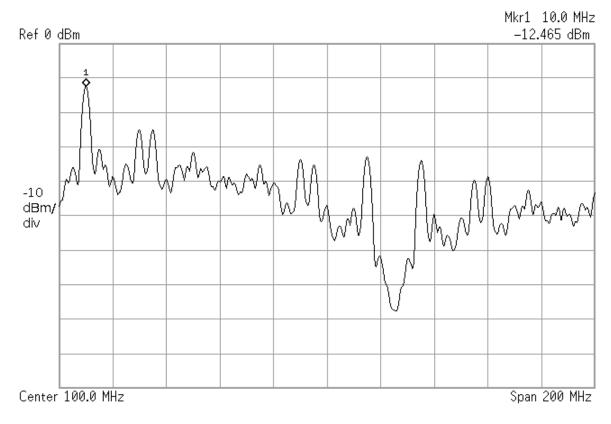

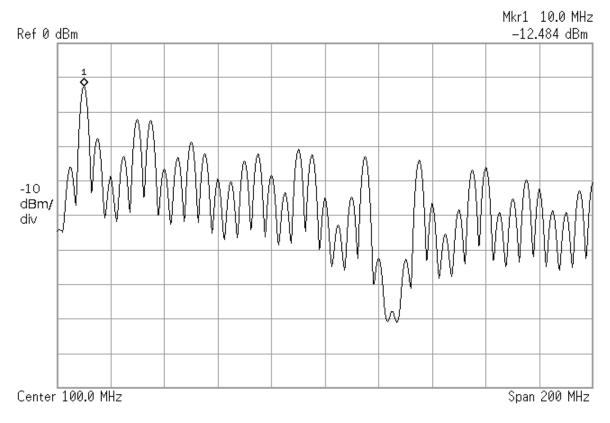

The results from these tests show that noise is only somewhat dependent on the shape of the distribution; the noise that is generated appears in a non-random fashion. Shown in Figure 6.11 is the average spectrum observed while testing the PN generator described in equation 6.33, and the results of the longer PN generator described in equation 6.26 are shown in the averaged Figure 6.12. The noise introduced by the longer PN sequence is approximately 2 dBm higher than the shorter sequence, however, discrete peaks of noise are clearly seen.

Figure 6.10: An Implementation of non–uniform sampling.

Figure 6.11: Output when equation 6.33 was implemented.

Figure 6.12: Output when equation 6.26 was implemented.

Figure 6.13: Output for 3 registers.

#### 6.5.2 Length of Shift Register

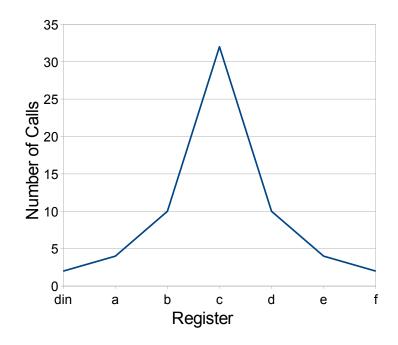

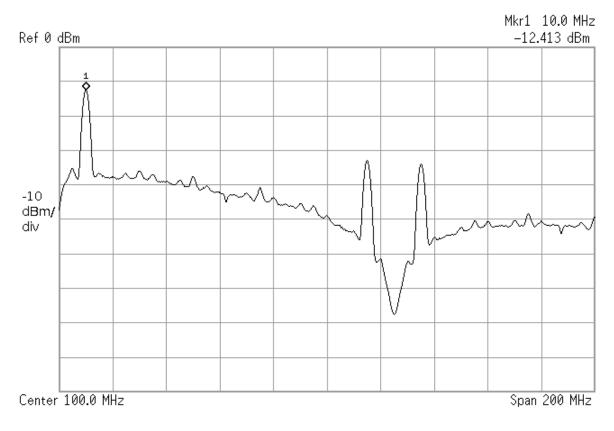

To test the effects changing the number of shift registers would have on the output, a uniform distribution was used when determining what register to take output from. Scenarios with 3, 5, 13 and 25 registers were tested. Varying the number of registers did have a profound impact on the channel being used during communication. As the number of registers increased, more noise was introduced to the channel. Figure 6.13 shows the output signal when there were 3 shift registers used, Figure 6.14 shows the output when 5 shift registers are used, and finally, Figure 6.15 show when there were 25 shift registers being used.

As seen in Figure 6.13, the added noise in minimal. For a 10 MHz signal sampled at 62.5 MHz, approximately half a wavelength was in the shift registers. Since the values that were resampled were taken from a local area, the noise introduced

Figure 6.14: Output for 5 registers.

was minimal.

Figure 6.14 represents a non–uniform sampling system with 5 shift registers. This allows for just less than a full wavelength in the shift registers. Because of this, the values that are written to the output have the potential to come from a slot almost a full wavelength away, the noise added is greater than before.

In the extreme case of having 25 shift registers, the non–uniform sampling module has the ability to hold 4 complete periods of signal in the shift registers at any time. Because the output can be driven from anywhere in the 4 wavelengths, the noise in the output can be seen in Figure 6.15 completely suppressing the 10 MHz test signal.

Figure 6.15: Output for 25 registers.

#### 6.5.3 Relation to Theoretical Results

To relate the theoretical results discussed in Section 6.1 to the observed results, the cases of 3 and 5 shift registers are used. In the case of 3 input registers, the input variance  $\sigma_i^2 = \frac{2}{3}$ . Applying the result found in equation 6.25, the output variance becomes  $\sigma_o^2 = \frac{1}{3}$ . Moving to the case with 5 registers used in the shift register, the input variance  $\sigma_i^2 = 2$ . Again, applying equation 6.25, the output variance becomes  $\sigma_o^2 = 1$ . The difference between the two theoretical output values is an increase of a factor of 3. When this difference is calculated on a logarithmic scale, the difference is represented as 4.8 dBm.

Looking at the screen capture results from both of those cases shown in Figure 6.13 and Figure 6.14, it is seen that the difference in noise level between those two tests was approximately 5 dBm. This matches closely with the theoretical result.

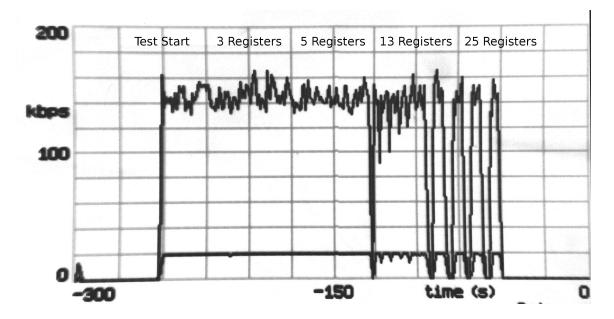

#### 6.5.4 Effect on CDMA/EVDO Traffic

Non-uniform sampling was gradually introduced into an RTAP data-transfer test using the same configuration as the pass-through tests performed in Section 5.5. For the most part, the CDMA/EVDO system was able to continue transferring with the noise introduced. Figure 6.16 shows the results of the no noise as well as the four different noise levels at 50 second intervals introduced in Section 6.5.2. The first section indicated, shows a normal data transfer, with no noise. When the minimum level of noise tested, represented by 3 registers with a uniform distribution, was suddenly introduced by toggling a switch there was no effect on the data transfer. Increasing the number of registers to 5 resulted in a delayed sudden drop in the data transfer, but the transfer immediately recovered and continued. When the number of registers was increased to 13, the transfer became intermittent as shown. Finally, when the shift register was increased to 25 registers, the transfer was immediately cut off. After testing the maximum level of noise, if the noise was not immediately

Figure 6.16: RTAP data transfer with non–uniform sampling noise added. Tests were done in 50 second intervals.

removed from the system after it was introduced, the connection would have to be reset; once the transfer had been sufficiently interrupted, the data connection was permanently lost. During power control tests, the open-loop power control test was repeated but was not able to respond within the envelope required. This was the case when any level of noise was introduced.

This test shows the resilience of the CDMA/EVDO standard against sudden increases in noise, and its ability to cope in order to continue to function. Also, an upper limit was found where the channel was dominated with noise in which no communication could take place. Because this noise was added in both the forward and reverse link, it is also possible that this is a limitation of the phone's ability to cope with the added noise.

### Chapter 7

## Summary and Future Work

### 7.1 Summary of Completed Work

This thesis provides a fully functioning cost–effective implementation of a means to access a communications medium to control the signal passing through it which is built using mostly COTS components. Tested first was the ability to receive and send a known signal, followed by receiving and sending CDMA/EVDO communications. This channel could be viewed using the SignalTap<sup>®</sup> facilities built into the FPGA, or using a splitter/combiner and a spectrum analyzer. The final implementation met all the requirements discussed in Section 2.2.

Intelligent selection of modulation and demodulation frequencies ensured that there was no interference with the removal of the LPF. By removing the LPF, the frequency range that can be used with this design is increased.

The discovery that the system would still work even when the communications were demodulated down to baseband and acquired by the FPGA in a laboratory setting was an interesting phenomenon. While the signal is being demodulated down to base band, a local fade appears near the DC point where the ADCs have a documented inability to resolve the signal. In this case, it is suspected that the ability for the base station and mobile to still exchange data is a result of the CDMA/EVDO standard and the implementation by the manufacturers being robust enough to handle these situations.

Non–uniform sampling was implemented to show that the system could introduce noise to the point where the power control algorithm used in the CDMA/EVDO implementation would fail and that the data transfer could be incrementally affected or stopped. During this investigation, the discovery that the non–uniform sampling would only increase the noise where a signal was present under certain conditions was made. A method of slowly introducing noise was also discussed; this is a low complexity method of introducing noise.

### 7.2 Future Work

In depth analysis of the aliasing that appeared during the non–uniform sampling was outside the scope of this thesis, and was only briefly investigated. Upon close inspection, it appeared that the noise introduced was somewhat ordered; the noise appeared to be made up of aliasing artifacts. This endeavour was undertaken to show that it was possible to affect the power control used in the system by introducing noise, and could be further researched.

Since this architecture is protocol agnostic it would be possible to test other wireless protocols. Tests do not need to be confined to verifying the power control algorithm; this architecture makes it possible to implement any test that requires unrestricted access to the communication channel. Similar tests could be performed on a mobile network based on most modern mobile radio systems.

## Bibliography

- T. Rappaport, Wireless Communications Principles and Practice. Prentice Hall Communications Engineering and Emerging Technologies Series, Upper Saddle River, NJ: Prentice Hall PTR, second ed., 2002.

- [2] T. Chulajata and H. Kwon, "Combinations of power controls for cdma2000 wireless communications system," Vehicular Technology Conference, 2000. IEEE VTS-Fall VTC 2000. 52nd, vol. 2, pp. 638–645, 2000.

- [3] M. Sim, E. Gunawan, C. Soh, and B. Soong, "Characteristics of closed loop power control algorithms for a cellular DS/CDMA system," *IEE Proceedings-Communications*, vol. 145, pp. 355–362, October 1998.

- [4] L. Korowajczuk, B. de Souza Abreu Xavier, A. M. F. Filho, L. Z. Ribeiro, C. Korowajczuk, and L. A. D. Silva, *Designing cdma2000 Systems*. John Wiley and Sons, Ltd., 2004.